# **Digital logic lab**

Digital logic lab equipped with a main unit and 13 experiment modules. Each module permits to realise several practical work. Supplied with leads and user's manual.

### ACCESSORIES SUPPLIED

Connect leads, 1,680 tie-point breadboard on top panel to be easily put into and taken off.

## 13 EXPERIMENT MODULES.

Designed with a 215 x 165 x 30mm solid body plastic housing, with electrical wiring printed on the front panel. An 8-bit DIP switch, located on the right top corner allows the user to simulate faults. Solution for faults are listed in the experiment manual for user's reference. Comprehensive experiment and instructor's manual are supplied with modules and contains theoretical drawings, wiring drawings. The experiment part has input signals, location of test points, tables to be filled up, comments and exercises.

ref. PSY3101

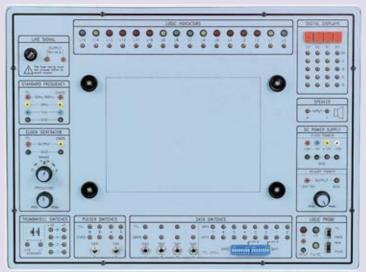

PSY3101 MAIN UNIT WITH:

- **4 fixed DC supplies** with output overload protection +5V -5V +12V -12V / 300mA on each output.

- 1 adjustable DC power supply with output overload protection: from 1.5 to 15V / 500mA

- **3 fixed frequencies:** 1Hz, 50Hz, 1MHz 0.01%, fanout : 10 TTL load **1 variable signal generator**

- 6 ranges from Hz to 1MHz Fanout: 10 TTL or CMOS load.

- **2 x 8 bit DIP switch**, 16 bit TTL level output

- 4 x toggle switch, each with debounce circuit.

- 1 fixed AC output 6Vrms with overload protection

Thumbwheel switch, 2 digit, BCD code output, common point input.

- 16 x LED indicating high and low logic state

- 4 sets of independent 7-segment LED display, with BCD.

- 3 x LED functioning as a logic probe. 1 speaker with driver circuit.

Dimensions : 400 x 300 x 130 mm. Weight : 5.8kg

Logic gates circuit, transistors, TTL and CMOS logic circuits. TTL/CMOS I/O voltage and current measurement experiments. Basic logic gate transmission delay measurement. AND, OR, NAND, NOR, XOR gate characteristics. Interface between logic gates.

ref. DIGITAL 1

NOR NAND gate circuits, XOR gate circuits, comparator circuit experiments, Schmitt gate circuit, open collector gate circuits.

ref. DIGITAL 2

Three-state gate circuit. Adder. Arithmetic logic unit. Bit parity generator.

ref. DIGITAL 3

Adder. Subtractor. 2 and 3 inputs reverser. BCD code adder circuit. Bit parity generator with XOR gate. 10 to 4 bit decoder with TTL IC.

ref. DIGITAL 4

4 to 2 bit encoder. 4 to 2 bit decoder. Decoder circuit experiments (decoding 7-segment display with BCD code).

ref. DIGITAL 5

Variable duty ratio oscillator. RS, T, D, JK flip flop. Preset left/right shift register circuit. Noise elimination circuit.

ref. DIGITAL 8

JK flip flop: asynchronous/synchronous, binaries up/ down bi-directional counters. Ring counter circuit, Johnson's counter circuit.

ref. DIGITAL 9

Construction dynamic scanning counter with single chip microprocessor. 8- bit converter circuit.

ref. DIGITAL12

Digital/analog converter circuit, unipolar and bipolar. 3 digits analog/digital converter circuit.

# ref. DIGITAL13

10 to 4 bit encoder. Multiplexer circuit experiments. Digitally controlled analog multiplexer/demultiplexer circuits. Bi-directional transmission with CMOS IC.

# ref. DIGITAL 6

Oscillator circuit with basic logic gates, with Schmitt gate. Voltage controlled oscillator circuit, with 555 trigger. Monostable multivibrator and synchronous astable multivibrator.

ref. DIGITAL 7

JK flip flop: asynchronous counter: decimal, divide by N, preset synchronous binary/decimal. Constructing ROM with diodes, with D flip flop. Constructing EPROM

ref. DIGITAL10

Constructing 64 bits RAM circuit. Constructing Electronic EPROM circuit

ref. DIGITAL11